whatapp/wechat:008618589033832

Skype:SannyDuanbsp

電力の完全性を確保するための3つの側面PCB設計

現代の電子設計では、電力の完全性はPCB設計の不可欠な部分です。電子デバイスの安定した動作とパフォーマンスを確保するには、電源から受信機に包括的に考慮して設計する必要があります。

パワーモジュール、内層面、電源チップを慎重に設計および最適化することにより、パワーの完全性を真に実現できます。この記事では、これら3つの重要な側面を掘り下げて、PCBデザイナーに実用的なガイダンスと戦略を提供します。

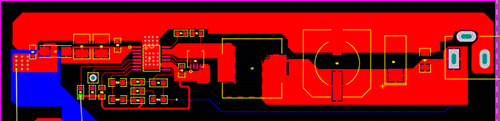

I.電源モジュールレイアウト配線

パワーモジュールはすべての電子デバイスのエネルギー源であり、そのパフォーマンスとレイアウトはシステム全体の安定性と効率に直接影響します。正しいレイアウトとルーティングは、ノイズ干渉を減らすだけでなく、滑らかな電流の流れを確保し、それによって全体的なパフォーマンスを改善することもできます。

2.パワーモジュールレイアウト

1.ソース処理:

パワーモジュールは、電力の出発点として機能するため、特に注意を払う必要があります。騒音の導入を減らすために、他の隣接を避けるために、パワーモジュールの周りの環境をできるだけきれいに保つ必要があります高周波またはノイズに敏感なコンポーネント。

2.電源チップへのクローズ:

パワーモジュールは、パワーサプライチップの近くに可能な限り配置する必要があります。これにより、現在の伝送プロセスの損失を減らし、内層平面の面積要件を減らすことができます。

3.散逸の考慮事項:

電源モジュールは、動作中に熱を発生させる可能性があるため、熱放散のためにその上に障害物がないことを確認する必要があります。必要に応じて、冷却のためにヒートシンクまたはファンを追加できます。

4.ループの回避:

ルーティングのときは、電磁干渉の可能性を減らすために電流ループを形成しないでください。

ii。内層平面設計計画

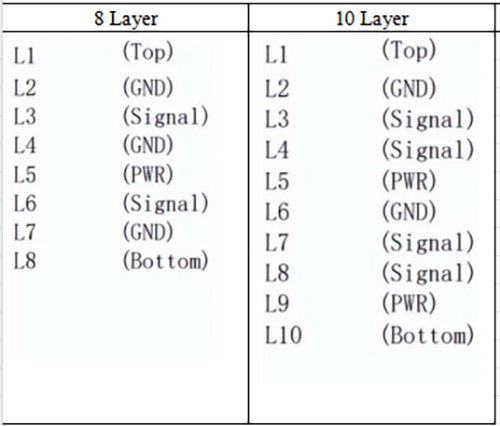

A.レイヤースタック設計

In PCB EMCデザイン、レイヤースタック設計は、ルーティングと配電を考慮する必要がある重要な要素です。

a。パワープレーンの低インピーダンス特性を確保し、地上騒音の結合を吸収するために、電力と地上飛行機の間の距離は10milを超えてはならず、通常は5mil未満であることが推奨されます。

b。単一の電源プレーンを実装できない場合、表面層を使用してパワープレーンをレイアウトできます。密接に隣接する電力と地上飛行機は、最小のACインピーダンスと優れた高周波特性を備えた平面コンデンサを形成します。

c。ノイズの結合を防ぐために、特に大きな電圧の違いがある隣接する2つの電力層を避けてください。避けられない場合は、2つの電力層の間の間隔を可能な限り増やします。

d。基準面、特に電力基準面は、低インピーダンス特性を維持する必要があり、バイパスコンデンサと層調整により最適化できます。

B.Multipleパワーセグメンテーション

a。特定のICチップのコア作業電圧などの特定の小さな範囲の電源の場合、パワー面の完全性を確保するために信号層に銅を置く必要がありますが、表面層に電力銅を敷設してノイズ放射を減らすことを避けます。

b。セグメンテーション幅の選択が適切なはずです。電圧が12Vを超える場合、幅は20〜30milになります。それ以外の場合は、12-20milを選択します。アナログとデジタルのパワーソースの間のセグメンテーション幅は、デジタル電源がアナログパワーに干渉するのを防ぐために増やす必要があります。

c。単純な電源ネットワークはルーティングレイヤーで完了する必要があり、長いパワーネットワークにフィルターコンデンサが追加される必要があります。

d。セグメント化されたパワープレーンは、共鳴を引き起こし、パワーインピーダンスの増加を引き起こす不規則な形状を避けるために定期的に保つ必要があります。長くて狭いストリップとダンベル型の部門は許可されていません。

C.プレーンフィルタリング

a。パワープレーンは、接地面と密接に結合する必要があります。

b。 500MHzを超える動作周波数のチップの場合、主に平面コンデンサフィルタリングに依存し、コンデンサフィルタリングの組み合わせを使用します。フィルタリング効果は、電力整合性シミュレーションによって確認する必要があります。

c。電力インピーダンスがターゲットインピーダンスよりも低いことを確認するために、コンデンサリードの拡大やコンデンサバイアスの増加など、コントロールプレーンのデカップリングコンデンサのインダクタを取り付けます。

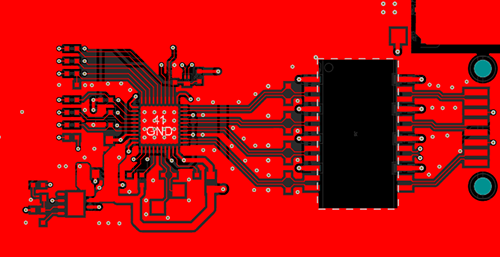

iii。パワーチップレイアウト配線

パワーチップは電子デバイスの中核であり、デバイスのパフォーマンスと安定性を改善するために、その電力の整合性を確保することが重要です。パワーチップの電力整合性制御には、主にチップパワーピンのルーティング処理と、デカップリングコンデンサの正しいレイアウトと配線が含まれます。以下は、これらの側面に関する考慮事項と実用的なアドバイスを詳述します。

A.chipパワーピンルーティング

チップパワーピンのルーティングは、電力整合性制御の重要な部分です。安定した電流供給を提供するには、一般的にチップピンと同じ幅まで電源ピンのルーティングを厚くすることをお勧めします。通常、最小幅8milを超えてはならないはずですが、より良い結果を得るには、10milの幅を達成してみてください。ルーティング幅を増やすことで、インピーダンスを減らすことができ、電力ノイズを減らし、チップへの十分な電流供給を確保します。

b。レイアウトとデカップリングコンデンサのルーティング

デカップリングコンデンサは、パワーチップのパワーインテグリティコントロールに重要な役割を果たします。コンデンサの特性と用途の要件に応じて、デカップリングコンデンサは一般に大小のコンデンサに分割されます。

a。大型コンデンサ:通常、大きなコンデンサはチップの周りに均等に分布しています。共振周波数が低く、フィルタリング半径が大きいため、低周波ノイズを効果的に除外し、安定した電源を提供できます。

b。小さなコンデンサ:小さなコンデンサは、より高い共振周波数とより小さなろ過半径を持っているため、チップピンにできるだけ近くに配置する必要があります。それらをあまりにも遠くに配置すると、高周波ノイズが効果的に除外されず、デカップリング効果が失われる場合があります。正しいレイアウトにより、高周波ノイズのフィルタリングにおける小さなコンデンサの有効性が完全に利用されます。

c。並列分離コンデンサの配線方法

パワーの完全性をさらに向上させるために、多くの場合、複数のデカップリングコンデンサが並行して接続されます。この慣行の主な目的は、並列接続を介して個々のコンデンサの同等のシリーズインダクタンス(ESL)を減らすことです。

複数のデカップリングコンデンサに並行する場合、コンデンサのVIASの配置に注意を払う必要があります。一般的な慣行は、力と地面のバイアスを相殺することです。これの主な目的は、デカップリングコンデンサ間の相互のインダクタンスを減らすことです。相互インダクタンスが単一のコンデンサのESLよりもはるかに小さいことを確認してください。そうすれば、複数のデカップリングコンデンサに並列に並列になった後のESLインピーダンス全体が1/nになります。相互のインダクタンスを減らすことにより、フィルタリング効率を効果的に強化し、電力安定性を改善します。

レイアウト電力モジュールのルーティング、内側の層平面設計計画、電源チップレイアウトと配線の正しい取り扱いは、電子デバイス設計では不可欠です。適切なレイアウトとルーティングを通じて、電力モジュールの安定性と効率を確保し、ノイズ干渉を減らし、全体的なパフォーマンスを向上させることができます。レイヤースタック設計と複数の電力セグメンテーション電力面の特性をさらに最適化し、電力ノイズ干渉を減らします。電源チップレイアウトの適切な取り扱いと配線とデカップリングコンデンサは、パワーインテグリティ制御に不可欠であり、安定した電流供給と効果的なノイズフィルタリング、デバイスの性能と安定性の向上を確保します。

実際の作業では、現在の大きさ、ルーティング幅、VIAの数、結合効果などのさまざまな要因を、合理的なレイアウトとルーティングの決定を行うために、包括的に考慮する必要があります。設計仕様とベストプラクティスに従って、電力の完全性の制御と最適化を確保します。この方法でのみ、電子デバイスに安定した効率的な電源を提供し、増加するパフォーマンスの需要を満たし、電子技術の開発と進歩を促進できます。

Shenzhen Anke Pcb Co.、Ltd

投稿時間:Mar-25-2024